Thiết kế mới dành trọng tâm cho hiệu năng.

Hai năm trước đây, nhà sản xuất chip x86 lớn thứ hai thế giới đã công bố thông tin về kiến trúc Bulldozer ("xe ủi") của mình trước thế giới tại Hot Chips 22. Hai năm sau, hãng này tiếp tục công bố thế hệ kiến trúc mới có tên Streamroller ("xe lu") tại Hot Chips 24. Liệu chiếc "xe lu" mới của AMD có giúp nhà sản xuất (NSX) chip này lấy lại được vị thế của mình sau thất bại của "xe ủi" trước "cầu cát" (Sandy Bridge)? Hãy cùng điểm lại những thay đổi của Streamroller lần này:

Đôi nét về "xe ủi"

"Xe lu" thực ra không phải một kiến trúc mới hoàn toàn bởi nó là bản nâng cấp dựa trên kiến trúc "xe ủi" của hai năm trước và gần đây là "xe đóng cọc" (Piledriver). Nên để hiểu về "xe lu", bạn cần nắm đôi nét của "xe ủi".

"Xe ủi" được xem là kiến trúc làm lại từ đầu của AMD sau một thời gian dài dùng kiến trúc K7/K8. Nhắc lại đôi chút về lịch sử, khi AMD ra mắt các chip K8 vào 2003, hãng này đã tạo tiếng vang lớn trong làng công nghệ vì các cải tiến mang tính đột phát về ý tưởng đã giúp dòng chip Athlon 64 (K8) vượt hơn đối thủ Pentium 4 dựa trên kiến trúc NetBurst của Intel lúc bấy giờ.

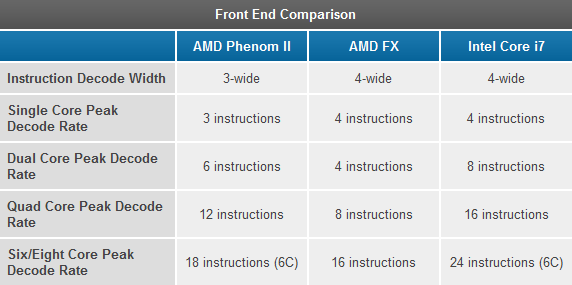

Kiến trúc K8/K10 của AMD chỉ đạt 3 IPC.

Ba năm sau, Intel mới trở lại được cuộc chiến khi giới thiệu dòng chip Core sử dụng kiến trúc cùng tên cũng là Core. Ngoài việc học tập những ý tưởng mà AMD dùng trên K8, Intel còn đẩy Core đi xa hơn khi áp dụng tăng năng lực tính toán của từng nhân x86 lên 4 IPC (các thiết kế trước đấy chỉ đạt 3 IPC). Cộng với một số cải tiến khác, kiến trúc Core cho thấy sự vượt trội của mình so với K8 và vị thế dẫn đầu trở về tay Intel. Các kiến trúc ra mắt sau này của Intel (trừ Atom) có thêm nhiều cải thiện nhưng nền tảng của chúng vẫn là kiến trúc Core ra mắt trong 2006.

Nhắc phần Intel là như thế, chúng ta quay lại phần AMD. Sau khi Intel dẫn đầu với kiến trúc Core, AMD vẫn tiếp tục dùng lại kiến trúc K8 nhưng thêm vào đấy một số cải thiện (cũng có tính cách mạng, ví như L3 cache) song căn bản không giúp AMD đối đầu về hiệu năng được với Intel. AMD thực sự cần một kiến trúc mới hơn.

Ý tưởng ban đầu của Xe ủi là 2 nhân riêng rẽ...

2010, các chi tiết về Xe ủi được công bố. Về mặt ý tưởng, Xe ủi có thể xem là đột phá lớn trong thiết kế chip khi đưa ra khái niệm "module". So với các thiết kế trước, mỗi nhân xử lý gần như độc lập lẫn nhau ở các chi tiết front-end (đầu vào), execution (xử lý) và một vài phần back-end (đầu ra) thì ở Xe ủi, cứ 2 nhân sẽ "xài chung" (share) một số thành phần. Theo mô tả của AMD, 2 nhân thuộc cùng 1 module Xe ủi sẽ dùng chung:

- Đầu vào - bộ nạp lệnh (fetch), bộ giải mã (decode)

- Xử lý - 1 nhân xử lý số thực (FPU) 256-bit dùng chung cho 2 nhân số nguyên (INT)

- Đầu ra - 2 nhân INT dùng chung 1 L2 Cache

... rồi khắc nhập khắc xuất thành 1 module.

Việc xài chung này nhằm giải quyết một bài toán mang tính "kinh tế": nếu nhân INT nào cũng được "vũ trang" đầy đủ mọi thành phần thì nó sẽ tốn rất nhiều silicon (chi phí tăng), kéo theo lượng điện tiêu thụ tăng tuyến tính. "Kết hôn" là giải pháp mà các kỹ sư AMD đưa ra nhằm tiết kiệm "tài nguyên" trong thời buổi vật giá leo thang. Các nghiên cứu xã hội cho thấy, một cặp vợ chồng chỉ tiêu thụ lượng tài nguyên bằng 1,5 người bình thường.

Dĩ nhiên, phải có đánh đổi. Chung một "mái nhà" sẽ xảy ra tình trạng xung đột về tài nguyên, nếu cả hai vợ chồng cùng phát sinh nhu cầu một lúc. Ví dụ một chiếc TV mà hai người coi, mỗi người một ý thích sẽ nảy sinh tranh cãi. Và đây là điều đã xảy ra với Xe ủi.

Hạn chế về IPC

Khi mới đọc tài liệu về Xe ủi, tôi chợt nhận ra rằng thiết kế này có "chút" vấn đề. Mặc dù các nhân INT có khả năng xử lý tới 4 IPC cùng lúc (tương đương các nhân Core) song đầu vào của chúng lại bị hạn chế. Một module Xe ủi chỉ có 1 bộ giải mã 4 hướng, bộ giải mã này xài chung cho cả 2 nhân INT. Tức nếu chỉ có 1 nhân hoạt động thì tối đa nó xử lý được 4 IPC. Nhưng nếu cả 2 nhân cùng hoạt động thì trung bình mỗi nhân chỉ đạt được 2 IPC (hoặc 3 & 1 IPC, hoặc 4 & 0 IPC).

Để bạn dễ hình dung, hãy liên tưởng tới dây chuyền sản xuất của nhà máy. Cho là 1 dây chuyền có thể cho ra tối đa 400 sản phẩm / ngày, với điều kiện có 40 lượt xe chuyên chở nguyên liệu đáp ứng được hết công suất của dây chuyền. Nếu chỉ 1 dây chuyền hoạt động thì 40 lượt xe này đều dồn vào đấy, nhưng 2 hoặc nhiều dây chuyền hơn cùng sản xuất thì chỉ có 20 hoặc 10 lượt xe đổ vào đấy, và sản lượng đầu ra chỉ đạt 200 hoặc 100 sản phẩm / ngày. Có nghĩa dây chuyền đang hoạt động dưới công suất. Đây là vấn đề của nhân INT trên Xe ủi.

Nếu chạy hết công xuất, 8 nhân Xe ủi cũng không lại 6 nhân K10 tại cùng xung nhịp!

Các kỹ sư AMD không nhận ra điều này sao? Có chứ, nhưng họ thiết kế "Xe ủi" với một nguyên tắc đánh đổi - tăng lượng nhân xử lý đến mức tối đa trong một khoản chi phí (transistor) có hạn. Một module Xe ủi gồm tất cả các thành phần trên (trừ L3 Cache, cầu bắc và trình điều khiển nhớ) tốn hết 213 triệu trans. Một con chip FX (Xe ủi) có đủ 8 nhân và 8 MB L3 Cache dùng hết 1,2 tỷ trans trên bàn giấy và 2 tỷ trans trên thực tế (?) Lý do của điều này tôi sẽ nói sau.

Tuy vậy, bạn cần hiểu rõ một chút về năng lực IPC (intrustion per cycle). Con số này ám chỉ hiệu năng của kiến trúc có thể xử lý được TỐI ĐA bao nhiêu tập lệnh trong một xung nhịp. Và đấy là giá trị TỐI ĐA, không có nghĩa mọi lúc đều đạt được như trên, có những lúc nhân xử lý chỉ đạt 1 hoặc 2 IPC. Lấy lại ví dụ về dây chuyền ở trên, có những thời điểm lượng đơn đặt hàng thấp, chỉ yêu cầu làm ra 100 sản phẩm / ngày (suy thoái kinh tế chẳng hạn) thì nhà máy hoạt động không hết khả năng. Đây là lý do mà Xe ủi yếu thế ở các ứng dụng đơn luồng (single thread), song ở đa luồng (multi-thread) lại rất có ưu thế.

Cải cách với "xe lu"

Con đường đi mà AMD chọn dường như khác với Intel. Thay vì làm ra con chip tốt hơn hẳn về mọi mặt như Core rồi tung ra thị trường thì AMD chọn hướng tốt hơn "chút chút" về ý tưởng rồi sau đấy... sửa dần dần! Cần nói thêm rằng chiếc Xe đóng cọc (Piledriver hiện có trên Trinity) cũng là một cải thiện so với Xe ủi, nhưng về mặt điện năng hơn là hiệu năng. Một review về nền tảng laptop Comal (Trinity) trước đây cho thấy Xe đóng cọc tiết kiệm điện hơn Xe ủi, trong khi kiến trúc không có nhiều thay đổi và đều dùng chung các transistor SOI 32nm.

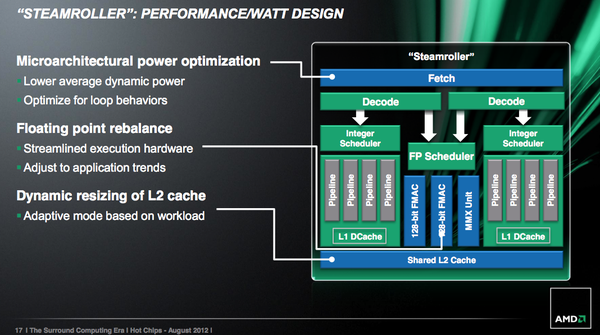

Mỗi INT nay có decoder riêng.

Và tới Xe lu, có vẻ vế hiệu năng sẽ được cải thiện, ít nhất là trên "giấy tờ" (tài liệu AMD công bố tại Hot Chips năm nay). Như đã nêu ở trên, nhân INT của Xe ủi bị "đói ăn". Xe lu sẽ khắc phục vấn đề này: thay vì chỉ có 1 bộ giải mã cho 2 nhân INT, nay mỗi nhân INT sẽ có bộ giải mã cho riêng nó. Có nghĩa lúc này 1 nhân INT Xe lu có thể chạy ở mức TỐI ĐA 4 IPC. Dù sao, hãy nhớ đấy là TỐI ĐA, không đồng nghĩa với hiệu năng sẽ gấp đôi.

Hiệu năng IPC không phải thứ duy nhất cần khắc phục ở Xe ủi. Vẫn còn vài thay đổi khác:

Cơ chế tiên đoán rẽ nhánh (branch prediction) tốt hơn

Vì để có mức xung cao, AMD đã chọn con đường ống lệnh (pipeline) dài giống như khi Intel đã làm với Netburst. Mặt trái của hướng đi này là nó cần một cơ chế tiên đoán chính xác. Vì nếu tiên đoán sai, cả một ống lệnh dài (tốn nhiều năng lực xử lý) sẽ trở nên vô ích. Các nhân INT phải tính toán lại từ đầu và hệ quả là hiệu năng chung giảm sút (thời gian xử lý tăng lên).

AMD không nói bộ tiên đoán trên Xe lu thay đổi như nào, chỉ nêu rằng nó sẽ đoán "sai" ít đi 20% so với Xe đóng cọc. Số lần "lỡ hẹn" (miss, ví dụ tập lệnh cần dùng đã bị xoá để dành chỗ cho tập lệnh mới) trên I-Cache (bộ đệm tập lệnh) cũng giảm đi 30%.

Tiêu giảm một phần FPU

Một vài thứ được tăng, đi kèm với vài thứ bị giảm. Bộ xử lý số thực (FPU) trên Xe lu bị giảm đi một đơn vị MMX. Lý do đằng sau hành động này là các đơn vị FMAC có thể chia sẻ một số phép toán với MMX. Tất nhiên có những trường hợp cần huy động tất cả các FMAC lẫn MMX tính toán sẽ nảy sinh vấn đề suy giảm hiệu năng. Song có vẻ các trường hợp như vậy rất hãn hữu (môi trường server hoặc HPC mới cần nhiều năng lực FPU) trong khi lượng silicon dùng cho FPU tốn kém khá nhiều.

Tăng không gian chứa, độ trễ không đổi

Trong quá trình tính toán, lượng dữ liệu phát sinh khá nhiều. Chúng cần được "cất tạm" vào nơi nào đó, đấy là các thanh ghi (register file hay RF). Lượng RF càng nhiều thì tính toán càng tiện, bù lại lượng silicon bỏ ra cũng tăng theo. AMD cho biết có tăng số RF trên Xe lu, chỉ không nói rõ là bao nhiêu.

Một chi tiết đáng chú ý là độ trễ (latency) của các bộ đệm không đổi. Trong quan điểm của AMD, vấn đề này không lớn. Hãy hình dung vấn đề như vầy: nhà máy A mất 2 ngày mới làm ra sản phẩm trong khi nhà máy B cần tới 4 ngày. Song 2 ngày của nhà máy A chỉ cho ra 200 sản phẩm, còn 4 ngày của nhà máy B cho ra 400 sản phẩm. Tức về cơ bản năng lực sản xuất của cả hai như nhau (400 sản phẩm / 4 ngày), song nhà máy A vẫn có lợi thế nếu đơn đặt hàng chỉ cho phép làm trong 3 ngày, mà số lượng hàng yêu cầu làm chỉ 100 sản phẩm.

Nhìn chung, AMD có triết lý của riêng họ, miễn tốt hơn Xe ủi là được.

Nỗ lực tiết kiệm điện

Trong khi thông tin về dây chuyền 20nm của Global Foundries (GF) lẫn TSMC - hai đối tác gia công chip cho AMD - vẫn im như tờ, hãng này chỉ có lựa chọn duy nhất là dây chuyền SOI 32nm hiện có của GF. Mặc dù dây chuyền Bulk 28nm đã có song về mặt điện năng không khác biệt so với SOI 32nm. Điều này có nghĩa Xe lu sẽ tốn điện hơn Xe ủi nếu chỉ tăng lượng trans mà không có biện pháp nào nhằm tiêu giảm điện năng.

May thay, kỹ sư của AMD đều là những người có trình độ. Dù toàn bộ con chip có ngần đấy trans, không có nghĩa lúc nào nó cũng cần chạy 100% số ấy. L3 Cache là một ví dụ, nó chỉ hữu ích trong các tải server hoặc ứng dụng nặng, ảo hoá... Các benchmark cho thấy các chip Phenom II chỉ nhanh hơn Athlon II khoảng 10% nhưng lượng L3 Cache là kích thước chip tăng lên 30 ~ 40%. Thông số này không có nghĩa chúng ta không cần trang bị L3 Cache cho Xe lu, mà là ý tưởng để thực hiện "Earth Hour" khi không cần thiết.

Xanh dương là các thành phần sẽ tham gia "Earth Hour".

Với Xe lu, AMD còn đẩy ý tưởng "Earth Hour" xa thêm một bước bằng cách tắt luôn cả bộ nạp lệnh (Fetching) hoặc FPU và L2 Cache nếu cần. Tắt Fetching trong trường hợp có những tập lệnh được dùng đi dùng lại (loop) nhiều lần (giống như công nhân được giao một việc làm đi làm lại suốt nhiều giờ liền). Tắt FPU trong các tác vụ phổ thông vì phần lớn chúng ta chỉ cần các nhân INT (môi trường laptop, desktop). Tương tự với L2 Cache nếu ứng dụng không nặng về mặt dữ liệu (cần nhiều bộ đệm để chứa).

Ngoài ra còn một biện pháp tiết kiệm điện khác mà đây là hệ quả từ "đám cưới" với ATI: dùng các thư viện thiết kế có mật độ cao. Nếu bạn chú ý, mật độ trans trên các chip Llano và Trinity của AMD cao đột biến so với các chip x86 thuần khác (nhất là của riêng AMD). Lý do? Các thư viện thiết kế của ATI "chặt" hơn so với của AMD (đây cũng là đặc trưng của các GPU). Một thiết kế của AMD có thể "phung phí" trans nhưng ATI lại "tiết kiệm" hơn. Đây là nguyên nhân mà bản thiết kế Xe ủi 8 nhân trên "bàn giấy" chỉ có 1,2 tỷ trans nhưng khi ra "thực tế' lại tới 2 tỷ trans - đã có một lượng lớn mạch điện không được thiết kế cẩn thận (bằng tay thay vì dùng máy làm tự động).

Llano có mật độ trans gần như kỷ lục.

Chi tiết này không có nghĩa AMD sẽ không dùng các công cụ thiết kế chip tự động (với số trans càng lớn thì tỷ lệ này càng cao). Hãng sẽ và còn tiếp tục dùng nếu lượng kỹ sư thiết kế bị cắt giảm hơn nữa (sau khi CEO mới lên đã có 1.300 nhân viên AMD bị thôi việc). Song hãy hy vọng rằng cách dùng các thư viện thiết kế sẵn có kia của AMD có thể hạn chế phần nào lượng trans (điện năng) thất thoát. AMD cho hay họ sẽ tiết kiệm được 15 - 30% điện năng so với Xe ủi.

Rốt cục chúng ta sẽ có gì?

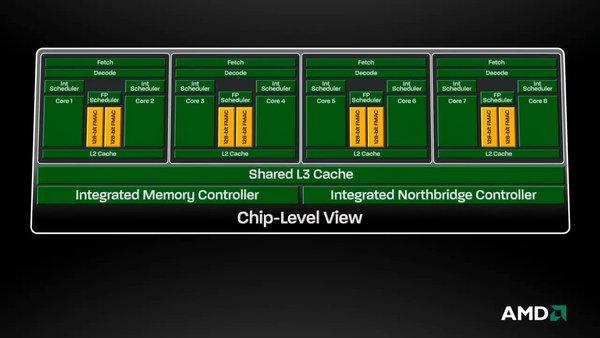

Ở phần đầu chúng ta đã nói, Xe lu sẽ không phải thiết kế mới hoàn toàn mà chỉ là cải tiến của Xe ủi hoặc Xe đóng cọc. Do vậy về cơ bản, sẽ không có nhiều khác biệt lắm về số lượng nhân, L3 Cache. Tức nhìn "xa xa" thì một chip Xe lu hoàn chỉnh sẽ tương tự như vầy (khác biệt ở số Decoder tăng gấp đôi). Nói cách khác, dự đoán chúng ta vẫn có một chip FX 8 nhân với 8 MB L3 Cache tương tự các bản Xe ủi hiện nay. Và vì không có nhiều thay đổi về "hạ tầng", có nhiều khả năng Xe lu vẫn dùng socket AM3+ trên nền chipset AMD 900 hiện có.

Chip Xe lu về tổng thể khá giống Xe ủi.

Song hy vọng với các thay đổi mà AMD cố gắng tạo ra, chúng ta sẽ lại thấy được cuộc đối đầu về hiệu năng giữa hai nhà khổng lồ x86, thay vì chỉ "một mình một ngựa" như hiện trạng với Intel. Dự kiến tới 2013, Xe lu sẽ xuất hiện cùng với Haswell.

Tham khảo AnandTech.