ARM, HP & Hynix gia nhập hiệp hội Hybrid Memory Cube cùng phát triển công nghệ bộ nhớ mới

| 29/06/2012 05:00 PM

Hybrid Memory Cube (HMC) có thể trở thành tương lai của các loại bộ nhớ máy tính.

Liên minh công nghiệp mới do Samsung & Micron cùng thành lập hồi tháng 10 năm ngoái, nay vừa kết nạp thêm 3 thành viên quan trọng mới - ARM, HP & Hynix - nâng tổng số các thành viên nòng cốt (developer) lên con số 10. Liên minh này có tên Hybrid Memory Cube Consortium (HMCC) và hiện đang có vài chục thành viên hưởng ứng (adopter) khác. HMCC ra đời với mục tiêu phát triển mô hình bộ nhớ HMC cũng như đưa nó đến với toàn ngành công nghiệp nói chung bằng cách quy tụ thêm nhiều hãng công nghệ cùng tham gia hỗ trợ.

HMC là gì? Đấy là một mô hình bộ nhớ mới, ban đầu được Intel và Micron đồng phát triển. HMC được đề ra trong bối cảnh kích thước transistor đang ngày một chạm tới giới hạn bán dẫn của nó và chúng ta cần một hình thái mới nhằm vẫn giữ được nhịp độ gia tăng dung lượng nhớ, băng thông dữ liệu nhưng lượng điện tiêu thụ vẫn hợp lý.

HMC dựa trên ý tưởng về các "toà nhà" bit nhớ.

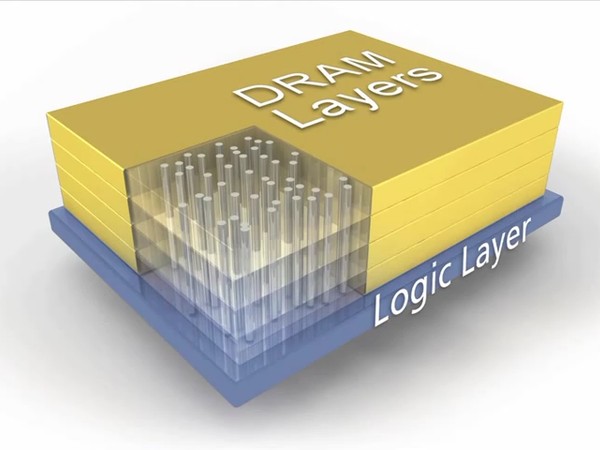

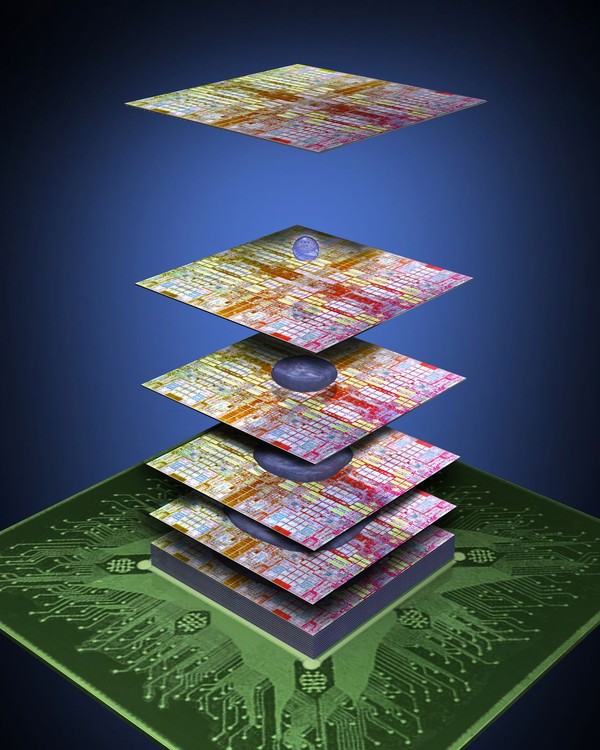

Để đạt được các yêu cầu nói trên, các kỹ sư phát triển HMC đã đề ra mô hình xây dựng chip nhớ mới. Thay vì tiếp tục tạo ra các tế bào nhớ theo chiều ngang (planar) như hiện nay, HMC dùng mô hình chiều dọc (vertical) để "chồng" (stack) các lớp DRAM lên nhau. Nhờ đấy mà diện tích các tế bào nhớ gần như không đổi trong khi mật độ dữ liệu tăng lên đáng kể. Bạn có thể hình dung mô hình này giống với các toà cao ốc văn phòng, tuy mặt bằng diện tích chung không đổi nhưng nhờ số tầng xây được mà không gian làm việc sẽ nhiều hơn so với các ngôi nhà chỉ có tầng trệt.

TSV hay 3D Stacking.

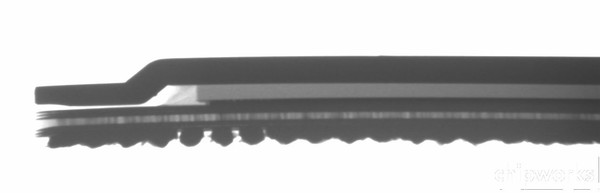

Cách thức chồng lớp này trong kỹ thuật bán dẫn có tên gọi through-silicon-via (TSV), hiện không chỉ được áp dụng trên chip nhớ mà với các chip xử lý, nó cũng được nhiều hãng công nghệ xem xét sử dụng. Lấy ví dụ, chip A5X của Apple là một thiết kế TSV với lớp DRAM nằm chồng lên lớp CPU. Bản thân IBM, hiện là một thành viên của HMCC, trước đây cũng từng demo một thiết kế TSV nhưng dùng một loại vật liệu liên kết mới kèm theo chức năng giải nhiệt. Sẽ không ngạc nhiên nếu loại vật liệu này được áp dụng cho công nghệ HMC.

Mặt cắt chip A5X với lớp DRAM nằm trên lớp CPU.

Giải nhiệt trên TSV là một thách thức lớn và IBM đang nghiên cứu hướng khắc phục.

Với lần kết nạp thành viên mới này, tương lai của HMC trở nên rộng mở hơn. Nếu Samsung & Micron là hai hãng sản xuất DRAM lớn thứ 1 & 3 thế giới, Hynix với tư cách là hãng DRAM lớn thứ 2 sẽ gần như đưa HMC lên thành chuẩn nhớ tương lai, vì tổng thị phần của 3 hãng này chiếm 80% toàn cầu. Còn HP là cái tên lớn ở mảng server. Cùng với IBM, sự hỗ trợ của HP dành cho HMC sẽ tạo ra cơ hội cho mô hình này tiến lên phân khúc điện toán cao cấp. Riêng với ARM, hãng chuyên về chip xử lý di động, khi mô hình HMC được chính thức hỗ trợ, bạn có thể hình dung ra những chiếc smartphone & tablet mới như thế nào.

Micron mô tả về HMC.

Theo Micron, HMC mang lại các lợi ích sau đây:

- Giảm thiểu độ trễ. Do nhiều die chip nằm chồng lên nhau, độ trễ khi truy cập tới một lượng bit nhớ lớn sẽ thấp hơn so với mô hình cũ

- Tăng cường băng thông. Một khối HMC có tốc độ gấp 15 lần một module DDR3

- Giảm thiểu điện năng. Mỗi bit trên HMC dùng ít điện thấp hơn 70% so với trên DDR3

- Chiếm ít không gian chứa. Kiến trúc chồng lớp của HMC dùng ít không gian hơn 90% so với các module RDIMM hiện nay

- Phù hợp với nhiều nền tảng điện toán. Tính cơ động về số lớp cho phép áp dụng HMC vào nhiều ứng dụng khác nhau

Tham khảo Micron & X-bit Labs.