Kiến trúc chip mới cho tablet của AMD sẽ có tính năng tương tự Ivy Bridge của Intel?

| 26/07/2012 0:00 AM

Gồm các tập lệnh chỉ có trên CPU cao cấp.

Các dòng chip tiết kiệm điện hiện nay của AMD (Brazos) lẫn Intel (Atom) vốn được dành riêng cho netbook hoặc tablet đều có đặc điểm chung là bị cắt giảm đi nhiều tính năng vốn chỉ có trên các chip cao cấp như Athlon, Phenom, FX hay Pentium, Core ix. Mục đích của việc này nhằm cắt giảm chi phí thiết kế, song bù lại khiến cho Brazos hoặc Atom bị sụt giảm hiệu năng đáng kể với những ứng dụng có hỗ trợ các tính năng trên. Trong một tiết lộ mới đây của AMD, có vẻ kiến trúc tiết kiệm điện mới của hãng này - Jaguar - sẽ khắc phục dần các nhược điểm trên.

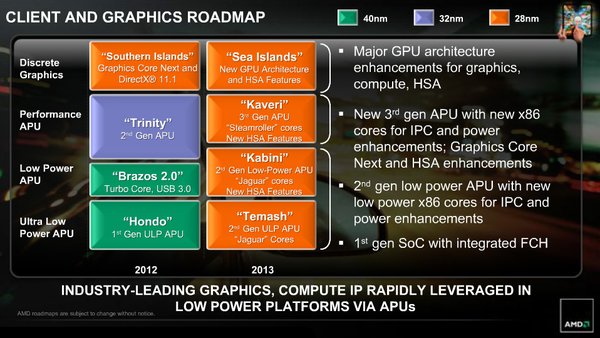

Jaguar là tên kiến trúc dùng cho 2013 của AMD, bên cạnh Steamroller. Steamroller sẽ dùng thay thế cho Piledriver hiện có trên chip Trinity còn Jaguar sẽ đảm nhận vị trí hiện giờ của Bobcat đang dùng cho Brazos lẫn Hondo. Có hai thiết kế chip sẽ hỗ trợ kiến trúc Jaguar là Temash (có khả năng dùng cho tablet) và Kabini (ưu tiên cho Ultrabook hoặc Sleekbook). Nét riêng của Bobcat lẫn Jaguar là chúng được tối ưu cho tiết kiệm điện.

Vì để tối ưu cho tiết kiệm điện, một số tính năng cao cấp đã bị cắt bỏ trên Bobcat lẫn Bonnell (kiến trúc hiện tại của Atom). Song nhờ sự tiến bộ của công nghệ bán dẫn (định luật Moore), nay các kỹ sư đã có thể bổ sung lại chúng lên các thiết kế chip mới này. Lấy ví dụ các thiết kế ARM mới đến từ Samsung, Qualcomm, NVIDIA, TI đều hứa hẹn sẽ gia tăng đáng kể hiệu năng. Điều tương tự với các đại diện x86 mà lần này là AMD. Vậy AMD đã bổ sung gì cho Jaguar?

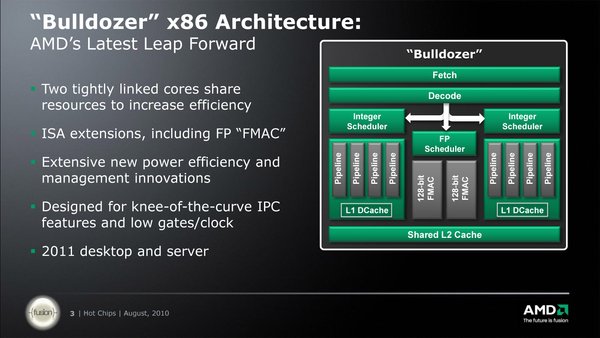

Kiến trúc Bulldozer của AMD có dạng module.

Đó là các tập lệnh SSE4.1, SSE4.2, AES, PCLMUL, AVX, BMI, F16C và MOVBE, hiện chỉ có trên kiến trúc Bulldozer / Piledriver của AMD hoặc Sandy Bridge / Ivy Bridge của Intel. Những ứng dụng có hỗ trợ các tập lệnh này thường cho tốc độ xử lý nhanh hơn các tập lệnh cũ.

Ngoài ra, đáng chú ý nhất trong đám trên là tập lệnh AVX vốn có bề rộng tới 256-bit. Để tính toán AVX, yêu cầu thiết kế chip phải có các khối xử lý số thực (FPU) có tổng bề rộng tương ứng. Tức Jaguar cần có tối thiểu 1 FPU 256-bit, hoặc 2 FPU 128-bit, hoặc 4 FPU 64-bit (lựa chọn này có thể không hay). Dựa vào Bulldozer, có khả năng AMD sẽ áp dụng thiết kế kiểu module (cứ 2 nhân số nguyên INT sẽ dùng chung 1 FPU) cho Jaguar nhằm cân bằng giữa việc cần đến nhiều FPU và chi phí silicon cần thiết. Hiện 1 nhân Bobcat gồm 1 INT và 1 FPU 128-bit. Rất có thể chip Temash và Kabibi sẽ có tối thiểu 2 nhân Jaguar với mỗi nhân có 1 FPU 128-bit và thiết kế dưới dạng module.

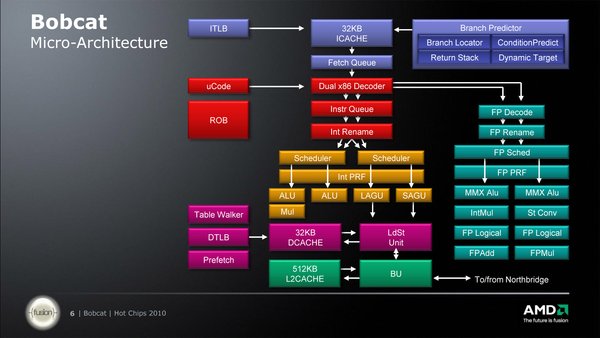

Kiến trúc Bobcat của AMD gồm một INT và một FPU.

Nếu giả định trên là đúng, dung lượng L2 cache trên Jaguar sẽ tăng cao hơn so với Bobcat. Một nền tảng Brazos 2 nhân hiện có tổng dung lượng L2 cache là 512 KB. Trong trường hợp Jaguar có dạng module, một chip Temash có thể L2 cache tới 2 MB và dùng chung cho cả 2 nhân. Và điều này đồng nghĩa với Jaguar sẽ là một cải thiện lớn về hiệu năng so với Bobcat.

Tham khảo X-bit Labs.